# Chapter .2

Algorithms and Design of the Common Fixed-Point Arithmetic Operations

## Addition Operation

Addition: is the most frequent operation performed by ALU. It also used for multiplication and division. Thus the speed of the adder unit is essential to the efficient operation of an execution unit.

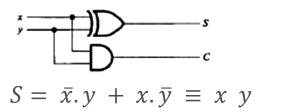

#### Half Adder (HA)

Half adder circuit has two inputs: A and B, which add two input digits

and generate a carry and sum.

| x | Half<br>Adder | <b>—</b> |

|---|---------------|----------|

| y | (HA)          | <b></b>  |

| Inp | <u>outs</u> | Outputs |   | Decimal<br>Value |

|-----|-------------|---------|---|------------------|

| x   | y           | C       | S |                  |

| 0   | 0           | 0       | 0 | 0                |

| 0   | 1           | 0       | 1 | 1                |

| 1   | 0           | 0       | 1 | 1                |

| 1   | 1           | 1       | 0 | 2                |

C = x.y

Figure: Half-adder

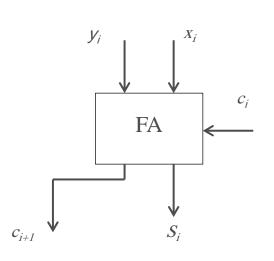

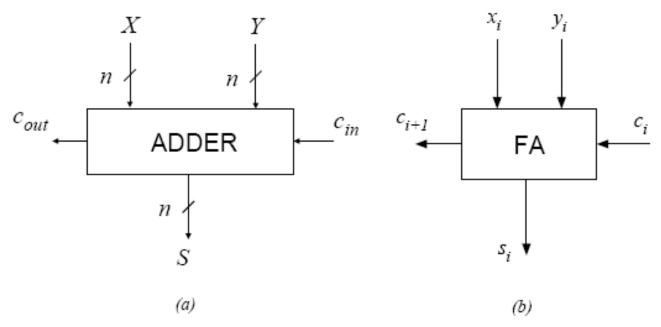

Full Adder (FA): is a combinational digital circuit with I/P bits  $x_i$  and  $y_i$  and incoming carry bit  $c_i$  and O/P sum bit  $s_i$  and outgoing carry bit  $c_{i+1}$

| $\mathbf{x_i}$ | y <sub>i</sub> | c <sub>i</sub> | $c_{i+1}$ | Si |

|----------------|----------------|----------------|-----------|----|

| 0              | 0              | 0              | 0         | 0  |

| 0              | 0              | 1              | 0         | 1  |

| 0              | 1              | 0              | 0         | 1  |

| 0              | 1              | 1              | 1         | 0  |

| 1              | 0              | 0              | 0         | 1  |

| 1              | 0              | 1              | 1         | 0  |

| 1              | 1              | 0              | 1         | 0  |

| 1              | 1              | 1              | 1         | 1  |

$$s_{i} = x_{i} y_{i}' c_{i}' + x_{i}' y_{i} c_{i}' + x_{i}' y_{i}' c_{i} + x_{i} y_{i} c_{i} \equiv x_{i} y_{i} c_{i}$$

$$c_{i+1} = x_{i} y_{i} + x_{i} c_{i} + y_{i} c_{i}$$

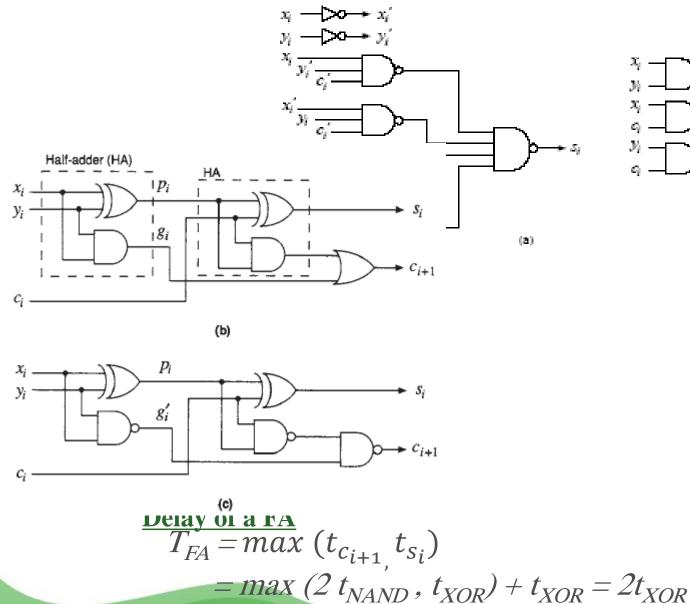

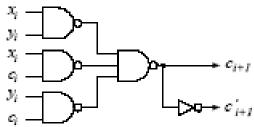

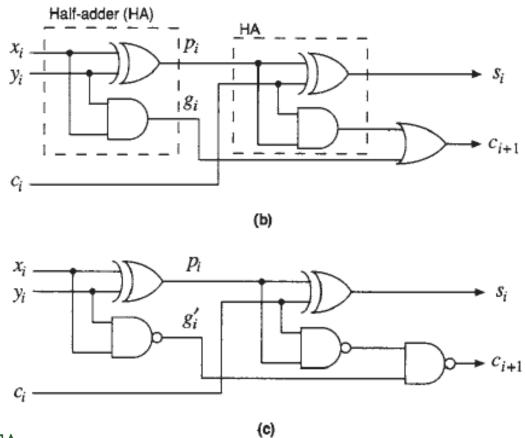

## Implementations of FA

### **Implementations of FA (continue)**

#### **Delay of a FA**

$$T_{FA} = max (t_{c_{i+1}}, t_{s_i})$$

$$= max (2 t_{NAND}, t_{XOR}) + t_{XOR} = 2t_{XOR}$$

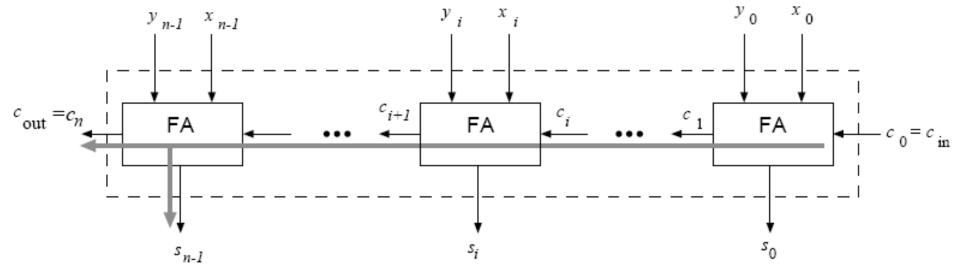

### Carry Ripple (propagate) Adder (CRA) or CPA

Ripple effect observed at sum outputs of adder until carry propagation is complete.

Fig.(2) a: An n- bit adder b: 1- bit adder (FA)

Figure: n- bit carry ripple adder (CRA)

The two (n- bit) operands (X and Y) are available at the same time.

\*The carries propagate from the FA in position 0 (with inputs are  $x_0$  and  $y_0$ ) to position i before that position produces correct sum and carry out bits.

The worst case delay (T<sub>CRA)</sub> of n-bit CRA

$$T_{CRA} = (n-1)t_c + \max(t_c, t_s)$$

$$= 2(n-1)t_{NAND} + \max(2t_{NAND}, t_{XOR}) + t_{XOR}$$

This is the delay of first XOR gate in the sum circuit

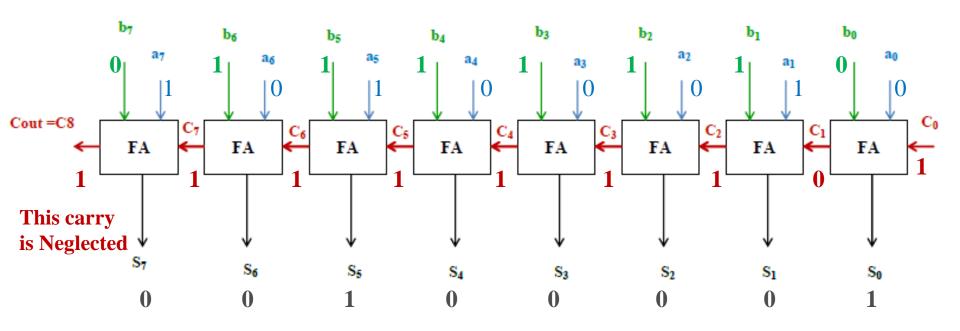

**Example:** Design an 8-bit CRA to add the following 2's complement numbers. Perform the addition on your design:  $A = -93_{10}$   $B = 126_{10}$

$$A = +93_{10} = (01011101)_2$$

Take 1's complement of A:  $A' = (10100010)$   $B = 126_{10} \equiv (011111110)_2$

Figure: 8- bit CRA

#### **Reducing the Adder Delay**

The delay of the CRA can be reduced by the following approaches:

- Reducing the carry delay  $t_c$ . This is achieved in the switched CRA called Manchester adder.

- Changing the linear factor (n) to a smaller factor (such as n/k or  $log_n$ ). This is achieved by the carry skip adder, carry lookahead adder, prefix adder, carry select adder, and conditional sum adder.

- Changing the number representation system.

## Carry Lookahead Adder (CLA)

The basic idea of CLA is to compute several carries, simultaneously. In the extreme, all carries could be computed at the same time.

Aside: The carry- out from a FA is:

$$c_{i+1} = x_i y_i + x_i c_i + y_i c_i$$

$$c_{i+1} = x_i y_i + (x_i + y_i) c_i$$

From this equation, we can see that there are three **mutually exclusive** cases. These cases depends only on the input operands bits  $(x_i \text{ and } y_i)$ .

Case 1: carry

$$c_{i+1}$$

generate if  $x_i = y_i = 1 \longrightarrow g_i = x_i$ . yi

Case 2: carry

$$c_i$$

is propagated if  $x_i$  or  $y_i \longrightarrow p_i = x_i \oplus y_i$

Case 3: carry

$$c_i$$

is killed if  $x_i = y_i = 0 \longrightarrow k_i = x_i'.y_i'$

Or is alive if  $a_i = k_i'$

\* Rewrite the carry- out of a FA:

$$c_{i+1} = g_i + a_i c_i$$

or  $c_{i+1} = g_i + p_i c_i$

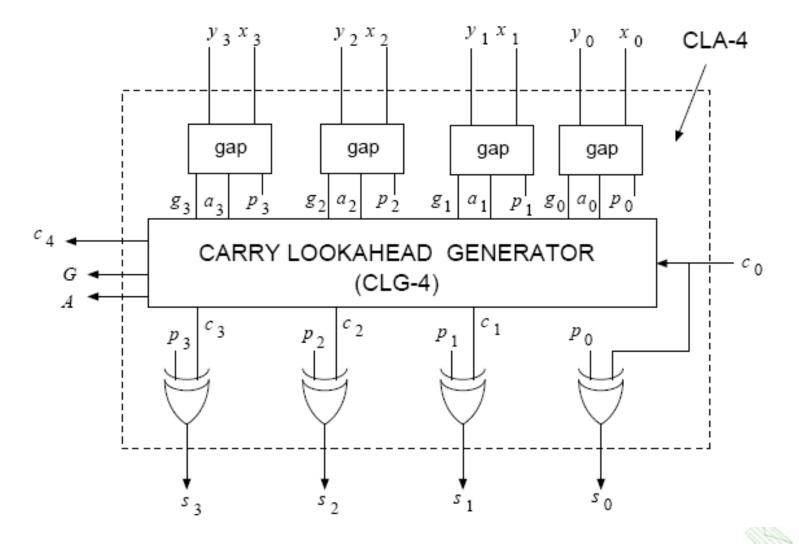

## (n- bit) CLA Addition

Using the previous equations of  $c_{i+1}$   $\longrightarrow$  all carries can be determined in parallel from the input data X and Y and forced carry  $C_0$ .

**Example:** Design a 4- bit CLA — the carry equations are:

$$c_{1} = g_{0} + c_{0} a_{0}$$

$$c_{2} = g_{1} + c_{1} a_{1} = g_{1} + g_{0} a_{1} + c_{0} a_{0} a_{1}$$

$$c_{3} = g_{2} + c_{2} a_{2} = g_{2} + g_{1} a_{2} + g_{0} a_{1} a_{2} + c_{0} a_{0} a_{1} a_{2}$$

$$c_{4} = g_{3} + c_{3} a_{3} = g_{3} + g_{2} a_{3} + g_{1} a_{2} a_{3} + g_{0} a_{1} a_{2} a_{3} + c_{0} a_{0} a_{1} a_{2}$$

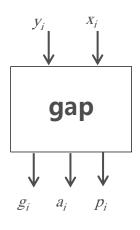

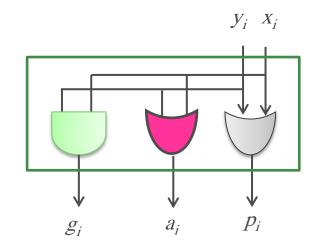

The internal design of a 4- bit CLA is:

Fig. (4)- bit CLA module (m=4)

Ex. Add  $X = 8_{10} = (1000)2$ , and  $Y = 9_{10} = (1001)2$

Figure: Internal logic design of gap circuit.

Where

A: is a carry alive signal of the group "m" (where m= 4-bit):  $A = A \underset{i=0}{\overset{m-1}{\triangleright}} a_i$

and G: is a carry generate signal of the group m (m= 4-bit):

$$G = OR \left( AND \atop j=0 \right) \left( AND \atop i=j+1 \right) g_i$$